みなさんこんにちは。テクノシェルパ技術コンサルタントの赤谷です。

みなさんこんにちは。テクノシェルパ技術コンサルタントの赤谷です。

7月になりむちゃくちゃ暑くなってきました。この時期、静かでエアコンが効いた当社電波暗室は、仕事に集中できる結構良い環境です。

さて、今回はノイズ対策の観点からシステムクロックの決め方について注意すべきポイントを簡単に解説いたします。

近年は様々な電子機器の処理能力がどんどん上がって、複雑なソフトウェア処理が短時間で行えるようになってきております。これはCPU、グラフィックコントローラ、メモリ周辺のチップセットが最適化(1チップ化など)するとともに、システムクロックの周波数が高くなり高速化していることが理由です。

では、そのシステムクロックが高ければ高いほど、良いのかというとそうではありません。

まず、周波数が高いと消費電力も増加します。デジタル回路はもともとロスが少ないものですが、スイッチングする際にわずかなリーク電流が発生します。数百MHzのシステムクロックの場合、1秒間に数百万回のスイッチングが繰り返されるわけですから、わずかなリーク電流も積み重なると、それ相応な消費電力となります。

よって、不必要に高いシステムクロックも良くないとわかります。

次にEMCの観点です。

システムクロックが高いとその倍数にあたる高い周波数の高調波が発生しますが、周波数が高いということは、波長が短くなり筐体のわずかな隙間からでもノイズが放射されます。波長の2分の1の隙間があるとノイズが放射されやすくなります。

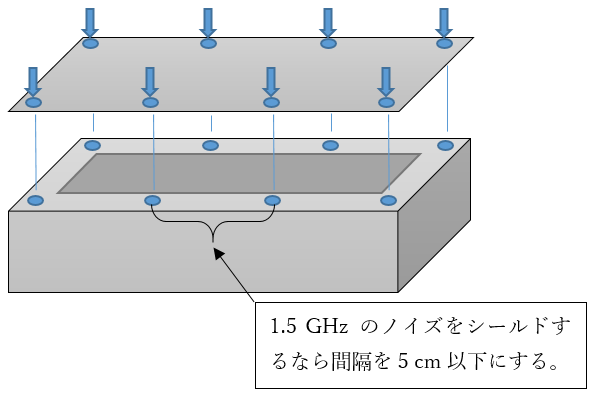

例えば1.5 GHzの信号の場合、波長は約20 cmですので10 cmの隙間があるとよくありません。

この隙間ですが、結構曲者なのです。

目に見える隙間はわかりやすいですが、EMCの観点では金属筐体同士接触しているように見えても導通がなく隙間とみなす必要がある場合があります。見た目は隙間なくきれいに接触しているように見えても、実際にはほとんどの場合、わずかな隙間があります。

このため、確実な導通を得るためにネジ止めを利用します。この時、ネジ止めの間隔は抑えようとするノイズ波長の4分の1以下にする必要があります。

このようにシステムクロックが高くなってくると、ノイズをシールドするにもコストが高くつきますので不必要にシステムクロックを高くするのは得策ではありません。

他にもEMCの観点でシステムクロックの決め方については重要なポイントがありますが、少々長くなってきましたので、それらはまた別の機会にご紹介させていただきます。

ノイズ対策でお困りの方はお気軽に弊社までお問合せください。

【関連リンク】