みなさん こんにちは!第一技術部 基板設計課の稲岡です。

みなさん こんにちは!第一技術部 基板設計課の稲岡です。

(当社の基板レイアウト設計受託サービスや半導体ベアチップを用いた基板設計/試作サービスの紹介はコチラ)

基板設計はガーバーデータを提出すれば、設計完了と思われがちですが、正確には、基板メーカーのCAM編集が完了しないと、「基板設計が完了した!」とは言えません。

基板メーカーは送付されたガーバーデータやドリルデータでそのまま製造する訳ではなく、基板メーカーの製造工程にあった調整が必要で、CAMにてデータの確認/編集を行います。基板製造上、不都合な点があった場合は、基板メーカーから問い合わせがあります。

このCAM編集に時間が掛かると、納期に影響がでるため、迅速な対応が求められます。

CAM編集時において、基板メーカーからの問い合わせ事例を紹介したいと思います。

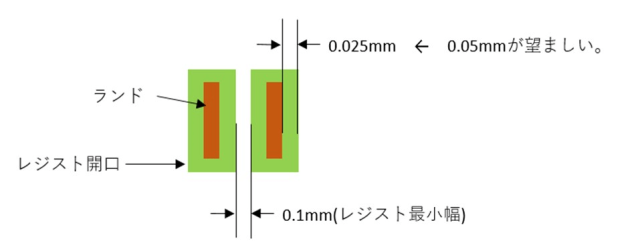

① ランド部におけるレジストクリアランス

【基板メーカー問い合わせ内容】

ランド部のレジスト逃げが片側0.025㎜しかありません。レジストずれ公差は、±0.05mmの範囲でランドにレジストが被ります。

【解説】

0.4mmピッチ以下のICに多くある事例です。

レジスト最小幅は0.1mm、レジストクリアランス公差が±0.05㎜の事例が多いですが、狭ピッチ部品の場合、両方を満足できないことがあります。

この場合、基板メーカーとレジスト幅や公差の見直しの交渉、基板メーカーの再選定、もしくは、ランド幅かレジストクリアランスのどちらかを優先する事になります。

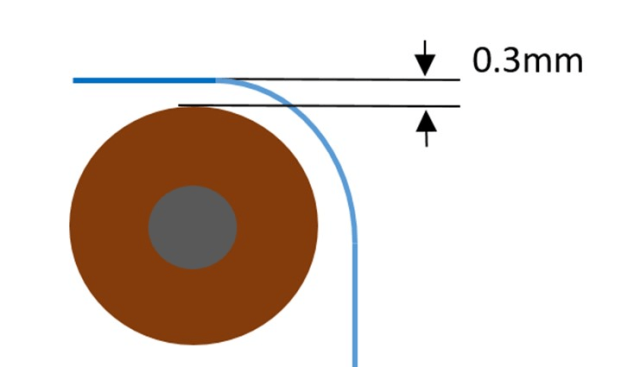

② 外形~銅箔までの距離

【基板メーカー問い合わせ内容】

外形~銅箔までの距離が弊社能力値の0.3㎜を下回る箇所があります。

【解説】

基板端の穴をFG(フレームグランド)にした場合などに起こる事があります。製造可能ですが、該当箇所にバリが発生する恐れがあります。バリの発生を前提にこのままとするか、設計変更する(クリアランスを増やす)かいずれかの対応をとる必要があります。

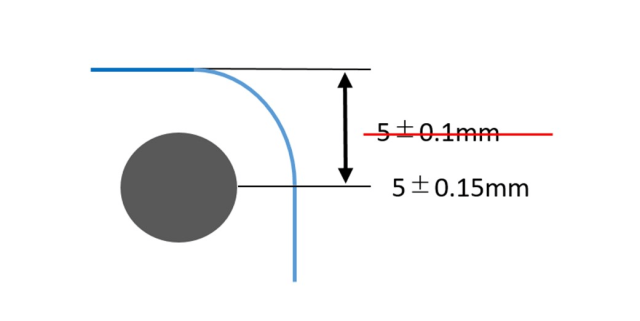

③ 外形寸法公差

【基板メーカー問い合わせ内容】

各寸法値を一般公差表に当てはめた場合、穴センター~外形間寸法公差が弊社工程能力外となります。こちら弊社標準公差±0.15㎜へ緩和頂けないでしょうか?

【解説】

外形図の公差は、機構担当が設定する事があり、この事例のように値が厳しい事があります。

製造着手前に外形図を基板メーカーに渡し、公差の確認を行いましょう。

いかがでしたでしょうか?皆様のご参考になれば幸いです。また、機会がありましたら、その他の事例も紹介したいと思います。

WTIでは様々な種類の基板設計や試作サービスを行っておりますので、お困りの際は、お気軽にお声掛けください。

【関連リンク】

【関連ブログ】

- 基板設計勉強中!(社内アンテナ講座編③)

- 半導体ベアチップを用いた評価基板の設計や試作もできるんです!

- 続・基板製造を考慮した設計

- 基板の製造方法の紹介

- 基板設計勉強中!(社内アンテナ講座編②)

- 基板設計勉強中!(社内アンテナ講座編①)

- 基板設計勉強中!(DRC編)

- 基板設計勉強中!(部品配置検討編)

- BGAの基板設計(その3)

- BGAの基板設計(その2)

- BGAの基板設計(その1)

- 基板設計の手順と入社2年目エンジニアの醍醐味!

- ついに導入しました!基板設計CAD『CR-8000 Design Force』

- 実は関係が深い?基板構造と部品パッケージ

- 知ってます?基板の種類と用途

- 特性インピーダンスと基板設計

- ガーバーデータで基板改版?

- 基板設計は回路設計者との以心伝心が大事!

WTIメールマガジンの配信(無料)

WTIエンジニアが携わる技術内容や日々の業務に関わる情報などを毎週お届けしているブログ記事は、メールマガジンでも購読できます。ブログのサンプル記事はこちら

WTIメールマガジンの登録・メールアドレス変更・配信停止はこちら

WTIの技術、設備、設計/開発会社の使い方、採用関連など、幅広い内容を動画で解説しています。