みなさん こんにちは!第一技術部 基板設計課の木戸です。

みなさん こんにちは!第一技術部 基板設計課の木戸です。

WTIでは汎用ICや受動部品を搭載した一般的なボードの設計や試作のほかに、あまり知られていませんが、大学や研究機関様向けに半導体のベアチップを用いた評価基板の設計や試作の対応も実施しております。

今回はこの内容についてご紹介させていただきます。

(当社の基板レイアウト設計受託や半導体ベアチップを用いた紹介はコチラ)

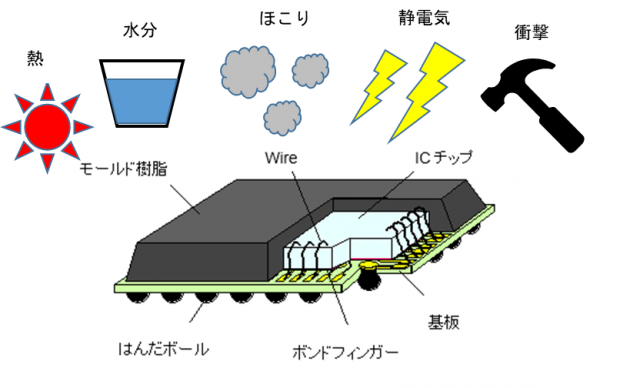

半導体ベアチップは、非常に小さく、薄いため、非常に壊れやすいです。

そのため、基板実装時の外力や外部環境(振動/衝撃や水分、静電気など)から守るため、リードフレームやBGAパッケージ基板などにベアチップを搭載し、樹脂モールド(パッケージング)して使用するのが一般的です。

(半導体パッケージに関するブログはコチラ)

半導体ベアチップを搭載するためのリードフレームやBGAパッケージ基板は、半導体メーカーが独自に開発していることが多く、汎用で簡単に調達できる物は、なかなかありません。

もし、見つけることができたとしても、新規に開発する半導体ベアチップはチップサイズやパッドサイズ、パット位置が様々なため、見つけたリードフレームやBGAパッケージ基板に、うまく半導体ベアチップを搭載できないということが発生します。

WTIではリードフレームやBGAパッケージ基板を新規設計し、試作メーカーと連携して、パッケージ試作を行うことも可能ですが、新規パッケージの開発は非常に高額となります。

また、大学や研究機関では研究目的のため、評価したい半導体ベアチップの試作の数量は少量であることが多く、その開発費用を考えると新規にパッケージを開発するには向いていません。

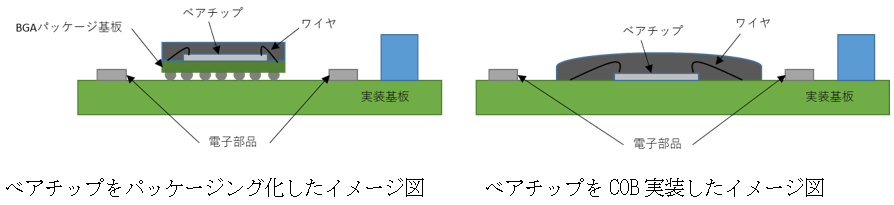

そこで、WTIでは、研究用の少量試作はパッケージングせずに、一般的なリジット基板を使用したCOB(Chip on board)をお勧めしております。

下図のように、リードフレームやBGAパッケージ基板の代わりに、一般的なリジット基板に直接半導体ベアチップを搭載、ワイヤボンディング後、ワイヤを保護(カバーやポッティング樹脂など)して評価基板に仕上げるイメージです。

様々な、設計/製造制約はありますが、新規パッケージ開発が不要なため、開発コストや工期を大幅に削減することが可能です。

お客様のご要求仕様に基づき、費用削減案や設計提案(チップのパッド配置など)も行わせていただいております。今回、ご紹介した半導体ベアチップのパッケージング、チップ評価ボードを必要とされるときはWTIに是非お声かけください。

【関連リンク】

【関連ブログ】

- 続・基板製造を考慮した設計

- 基板の製造方法の紹介

- 基板設計勉強中!(社内アンテナ講座編②)

- 基板設計勉強中!(社内アンテナ講座編①)

- 基板設計勉強中!(DRC編)

- 基板設計勉強中!(部品配置検討編)

- BGAの基板設計(その3)

- BGAの基板設計(その2)

- BGAの基板設計(その1)

- 基板設計の手順と入社2年目エンジニアの醍醐味!

- ついに導入しました!基板設計CAD『CR-8000 Design Force』

- 実は関係が深い?基板構造と部品パッケージ

- 知ってます?基板の種類と用途

- 特性インピーダンスと基板設計

- ガーバーデータで基板改版?

- 基板設計は回路設計者との以心伝心が大事!

WTIメールマガジンの配信(無料)

WTIエンジニアが携わる技術内容や日々の業務に関わる情報などを毎週お届けしているブログ記事は、メールマガジンでも購読できます。ブログのサンプル記事はこちら

WTIメールマガジンの登録・メールアドレス変更・配信停止はこちら

WTIの技術、設備、設計/開発会社の使い方、採用関連など、幅広い内容を動画で解説しています。