みなさん、こんにちは。第一技術部の赤谷です。

みなさん、こんにちは。第一技術部の赤谷です。

前回のブログ「非同期入力はメタステーブル対策が必要」では、非同期信号の入力タイミングによっては、メタステーブルが発生し不具合を起こす可能性について解説しました。

今回は、そのことに関連しFPGAの設計ではタイミング検証が極めて大事であることをお伝えしたいと思います。(当社のFPGA設計受託サービスはコチラ)

FPGAはデジタル回路をプログラミングできる非常に便利なデバイスですが、何も無いところに突如として回路が現れる訳ではありません。当然ですよね。

FPGAには論理回路やフリップフロップ(FF)などの基本回路がまとまった「基本セル」と呼ばれるブロックがびっしり詰まっており、この基本セル間の配線をプログラミングすることによって目的の回路を構成します。配線をプログラミングによってオンあるいはオフするイメージです。

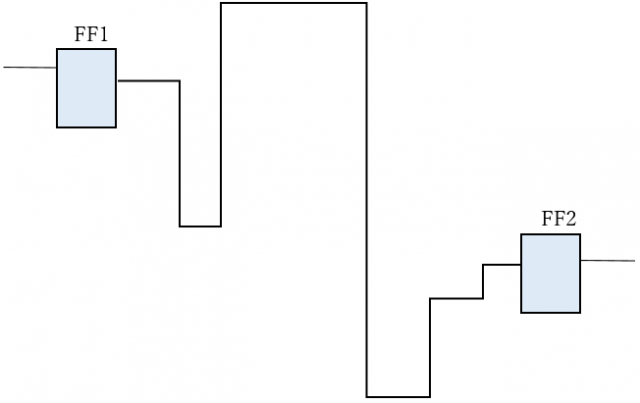

よって、回路規模が大きくFPGAのリソースを多く使用しているような場合には、余っている基本セルを見つけ出し配線することになるため、配線が思わぬ長さとなることがあります。

フリップフロップ間の配線が長いイメージ

配線が長くなると当然ながら電気信号も遅延してしまいます。

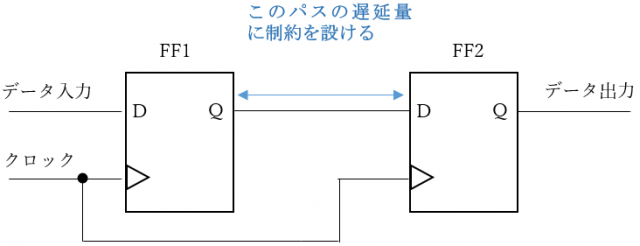

例えば、システムクロックが100 MHzの場合、1サイクルが10 nsであるため、単純に考えて10 ns以上遅れると信号を正しく伝達できないと分かりますよね。

実際には、出力側フリップフロップ(上図のFF1)による遅延と入力側フリップフロップ(上図のFF2)に必要なセットアップタイムなどがあるため、許容される配線遅延は10 nsより小さくなります。

このように期待するシステムクロックで回路を正しく動作させるためには、配線遅延について制約を設ける必要があります。

このタイミング制約はFPGAベンダーが提供する開発ツール上の制約ファイルにて設定します。システムクロックが100 MHzでデューティー比50 %の場合の設定は次のような感じです。

NET "FPGA_CLKIO" TNM_NET = "sys_FPGA_CLKIO";

TIMESPEC TS_sys_FPGA_CLKIO = PERIOD "sys_FPGA_CLKIO" 100MHz HIGH 50 %;

このような設定を行った上でFPGA開発ツールによって配置配線を実行します。

配置配線の結果はレポートとして出力されるため、タイミングエラーが無いか良く確認することが大切です。

今回、ご紹介したタイミング制約は、ほんの一例です。実際のFPGA開発では、入力回路のパス、出力回路のパスなど様々なパスについてタイミング制約を設ける必要があります。

これらについては、またの機会にご紹介します。

FPGAはVHDLやVerilog-HDLなどのプログラミング言語を習得すると、あまりハードウェアの知識がなくても論理回路を作ることができます。(論理回路は開発ツールが頑張って構成してくれますので。)

それが故にハードウェア設計の基本であるタイミング検証などがおざなりになり、思わぬ不具合を招くことがあります。

このようなことが無いようにFPGA開発では、ハードウェアの視点で正しく設計できているかしっかりチェックを行うことが大切です。

WTIにはFPGA設計受託サービスもございますので、今回ご紹介したタイミング制約などでお困りの際はお気軽にお問い合わせ下さい。

【関連リンク】

- 電気設計受託サービス

- FPGA設計受託サービス

- サブスクエンジニアリングサービス(定額エンジニアリングサービス)

- マイコンなのかFPGAなのか ~システム設計のポイント~

- FPGAとは? ~FPGAってどんなもの? どこに使われているの?~

- そのお困りごとはFPGAで解決できるかもしれません

WTIメールマガジンの配信(無料)

WTIエンジニアが携わる技術内容や日々の業務に関わる情報などを毎週お届けしているブログ記事は、メールマガジンでも購読できます。ブログのサンプル記事はこちら

WTIメールマガジンの登録・メールアドレス変更・配信停止はこちら

WTIの技術、設備、設計/開発会社の使い方、採用関連など、幅広い内容を動画で解説しています。