新年あけましておめでとうございます。第一技術部の赤谷です。

新年あけましておめでとうございます。第一技術部の赤谷です。

昨年10月の「パーシャルパワーダウン時に重要なIoff機能」以来のブログ投稿となります。

本年もエンジニアの皆様にとってのお役立ち情報をブログで配信していこうと思っておりますので、どうぞよろしくお願いします。

今回のブログでは、FPGA などのデジタル回路設計で重要となる 非同期入力に起因するメタステーブル問題 について解説します。

メタステーブルは発生頻度が低いものの、原因調査が非常に難しい厄介な問題です。

その仕組みと対策を理解しておくことは、安定した回路設計に欠かせません。

クロック同期回路ではタイミング規定を守ることが大事

同期回路で必要となるセットアップタイムとホールドタイムの基礎

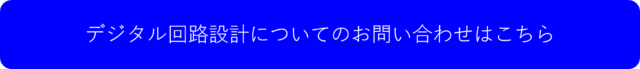

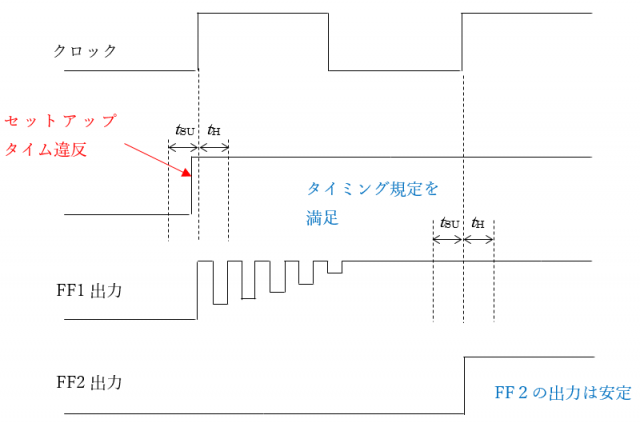

デジタル回路には、クロックに同期した回路(同期回路)とそうではない回路(非同期回路)があります。同期回路で使用されるフリップフロップ(FF)は、安定動作の要件としてセットアップタイム(tSU)とホールドタイム(tH)が定義されています。

フリップフロップの入力タイミング

上図の通り、入力信号はクロック立ち上がりの前後で規定時間以上安定している必要があります。

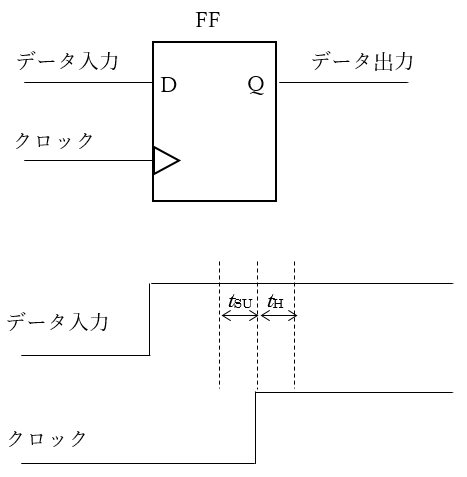

タイミング規定を満たさない場合に起こる問題点

セットアップタイム(tSU)またはホールドタイム(tH)の規定を満たさない場合、フリップフロップの出力信号は一定期間発振した状態(メタステーブル)になる可能性があります。この不安定な状態が後段回路に伝わると、論理誤動作の原因になります。

メタステーブルとはどのような状態か?またその条件とは

メタステーブル状態が発生する仕組み

メタステーブル状態

セットアップタイム違反が発生した場合、フリップフロップの内部ゲインが確定できず、出力が一定期間不安定な状態に陥ります。この状態がメタステーブルです。

非同期入力ではメタステーブルが避けられない

外部信号などの非同期入力では、データタイミングをクロックと合わせることができないため、メタステーブルは確率的に必ず発生します。

したがって、非同期入力では「発生をゼロにする」よりも「発生しても回路動作に影響させない」設計が重要です。

非同期入力におけるメタステーブル対策 --回路構成について--

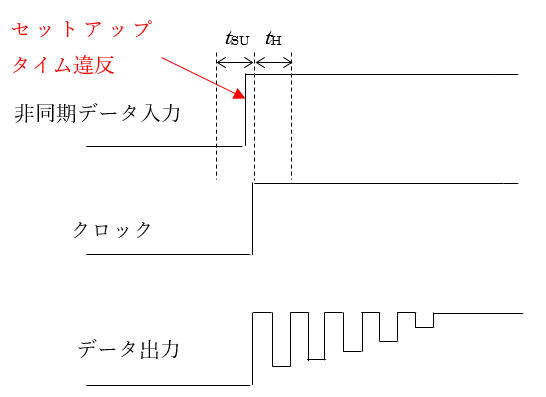

二段フリップフロップによる同期化処理

最も基本的な対策は 二段のフリップフロップを直列に配置する同期化回路 です。

メタステーブルは一定時間で収束するため、一段目で発生しても次のクロックには安定し、二段目の出力は安定します。

メタステーブル対策回路

メタステーブル対策回路のタイミング図

システムクロックが高速である場合の追加対策

ただし、システムクロックが高速である場合は、メタステーブルが収束しないまま、二段目のフリップフロップにも伝搬する可能性があります。このような場合は、もう一段フリップフロップを追加しておく方が安全です。どの程度でメタステーブルが収束するかについては、正確なデータはありませんが、だいたい10~12 ns以内には収束するようですので、システムクロックがおよそ80 MHz以上の場合は、もう一段フリップフロップを入れておく方が無難です。

非同期入力におけるメタステーブル対策 --レイテンシーとの関係性--

フリップフロップ段数とレイテンシーのトレードオフ

「じゃあ最初から多めにフリップフロップを入れておけば良いじゃないか」と思われるかも知れませんが、フリップフロップを一段追加毎にクロック1サイクル分の遅延(レイテンシー)が発生しますので、求められる処理速度や回路のリソースに応じてフリップフロップの段数は最適化する必要があります。

最適な同期段数を決める際の設計判断基準

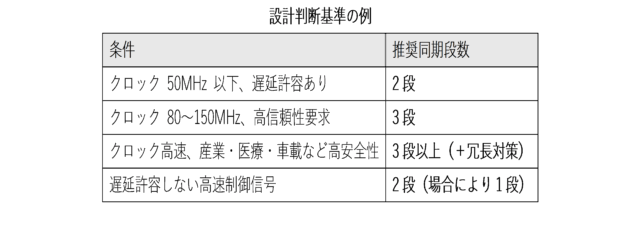

ざっくりした設計判断基準は以下のようになります。

最適な同期段数は、クロック速度・安全性要求・遅延許容範囲・リソース状況 を総合的に見て判断します。

まとめと当社のサポート

このメタステーブルに起因する問題は、多くのエンジニアが陥るもので、その不具合については発生頻度が低く、原因調査など非常に苦労する厄介なものです。よって、設計段階でメタステーブル対策をきっちり行っておくことが大切です。

当社はこのような論理回路設計の基礎をきっちり抑えたエンジニアが揃っておりますので、FPGAなどの動作不具合でお困りの際は、是非お問い合わせ下さい。

【関連リンク】

- 採用情報

- 電気設計受託サービス

- FPGA設計受託サービス

- サブスクエンジニアリングサービス(定額エンジニアリングサービス)

- マイコンなのかFPGAなのか ~システム設計のポイント~

- FPGAとは? ~FPGAってどんなもの? どこに使われているの?~

- そのお困りごとはFPGAで解決できるかもしれません

- 人材採用(インターンシップ・新卒・中途)