みなさん、こんにちは。

みなさん、こんにちは。

パワーデバイス設計課の中松です。

前回のブログでお話ししたパワーMOSFETのアバランシェ耐量試験の続きです。

前回、アバランシェエネルギーが同じであっても、試験条件が異なればMOSFETのジャンクション温度Tjは異なるため、単純に比較できないことをご説明しました。では、前回と同じデバイスで、L負荷の値L=3 µH、アバランシェ電流IAS=50 Aの場合(ケース③)を考えてみましょう。

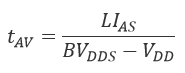

アバランシェ期間の時間tAVは

であったため、アバランシェ電圧BVDSS=600 V、電源電圧VDD=300 Vとすると、ケース③ではtAV=500 nsになります。(この値は現実的ではありませんが、このまま進めます。)

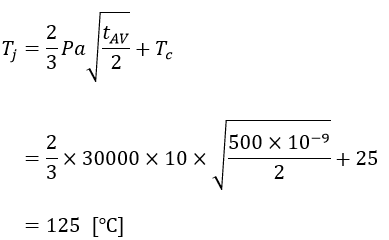

前回の式を用いてTjを計算すると

になります。つまり、前回までのお話ではTjは150℃を下回っているので、アバランシェエネルギーEASは問題ないことになります。ところが、実際にアバランシェ耐量試験を行ってみると、IAS=50 AでMOSFETが破壊してしまいました。それはなぜでしょうか。

実は、前回まではエネルギーによる破壊モードを考えていましたが、その他にも電流で破壊するモードがあります。

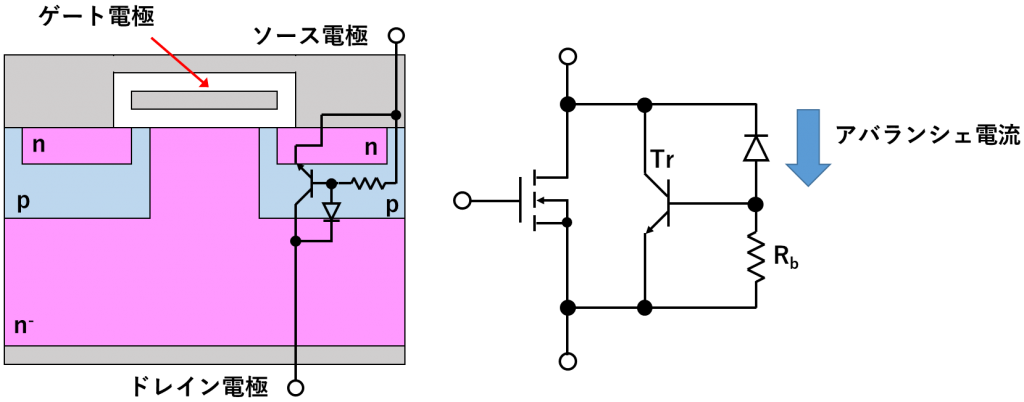

図1にnチャネルパワーMOSFETの構造と等価回路を示します。構造上、nチャネルMOSFET には寄生のnpnトランジスタTrと寄生ダイオードDが存在しており、通常はこのトランジスタTrがオンしないように設計されています。しかし、高電圧印加などによってMOSFETの寄生ダイオードDがアバランシェ動作した際には、抵抗Rbにアバランシェ電流が流れ、Rbに電位差VRbを生じます。この電位差VRbが大きくなると寄生トランジスタTrのベースにもアバランシェ電流が流れ、寄生トランジスタTrがオンしてしまい、Trのコレクタからエミッタに大きな電流が流れデバイスが破壊に至ります。これが電流で破壊するモードの原理です。

図 1 nチャネルMOSFETの構造と寄生トランジスタ

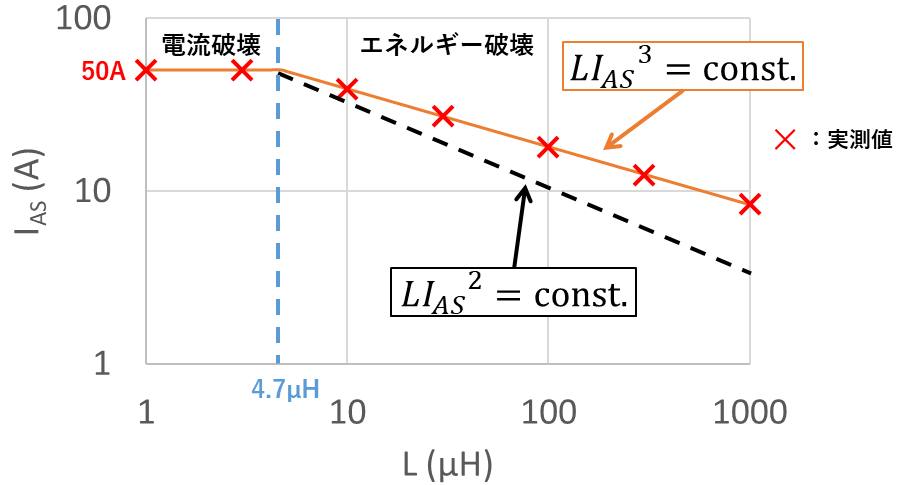

破壊モードを切り分け、アバランシェ耐量の実力値を調べるために、Lの条件を振って測定し、破壊したときのIAS値をLとIASの両対数グラフ上にプロットすることがよく行われます。

図2は今回の素子で測定した場合の例になります。赤い×印が実測値で、オレンジ色のラインは補完した結果です。(今回、エネルギー破壊側は破壊する実力値ではなく、Tjが150℃になるラインでプロットしていますが。)

図 2 アバランシェ破壊時のLとIASの関係

Lが4.7 µH以下の領域ではIASはほぼ一定であり、電流破壊であることを示しています。一方でLが4.7 µH以上の領域ではグラフの傾きは-1/3であり、IASはLの1/3乗に反比例していることがわかります。つまり、この領域ではエネルギー破壊であることを示しています。このように、L負荷の条件を振って測定することで、破壊モードを切り分け、各L負荷の値でアバランシェ耐量を推定することができます。

当社には、パワーデバイスの特殊な試験環境と、特殊な試験に対応できるエンジニアがいますので、アバランシェ耐量試験をはじめとする各種パワーデバイスの評価を必要とされる場合は、是非ご相談ください。

【関連リンク】

関連サービス

- パワーモジュール評価サービス スイッチング評価 短絡耐量試験 静特性評価 端子間容量測定

- カスタム計測・受託評価 パワーサイクル試験

- 環境負荷物質調査(chemSHERPA)の代行サービス

- オンデマンド講座 パワーデバイスの基礎

- ライブ配信講座 パワーデバイスの基礎

関連ブログ

- パワーMOSFETのアバランシェ試験とは ~その2~

- パワーMOSFETのアバランシェ試験とは ~その1~

- パワーデバイスの短絡試験について

- オシロスコープの基礎知識

- パワー半導体の評価は安全が第一!

- SiC, GaN, Ga2O3パワーデバイス・モジュール開発が活発化!? でも、課題もあります

- 「パワー半導体」とは何か? ~パワー半導体で地球環境を救う!~

- いまさらなんですが、SiCって何がいいのでしょうか?

- パワーエレクトロニクスって、どういうもの?

WTIメールマガジンの配信(無料)

WTIエンジニアが携わる技術内容や日々の業務に関わる情報などを毎週お届けしているブログ記事は、メールマガジンでも購読できます。ブログのサンプル記事はこちら

WTIメールマガジンの登録・メールアドレス変更・配信停止はこちら

WTIの技術、設備、設計/開発会社の使い方、採用関連など、幅広い内容を動画で解説しています。