みなさん、はじめまして。

みなさん、はじめまして。

パワーデバイス設計課の中松です。

私は主にパワーデバイス(パワーMOSFET、IGBTのディスクリート品やモジュール品)の評価を行っています。

今回はパワーデバイスの短絡試験についてお話ししたいと思います。

(スイッチングによる短絡耐量試験サービスはこちら)

パワーデバイスの短絡とは、高電圧が印加されている状態でパワーデバイスがオンし、導通状態になって大電流が流れることです。

インバータ等のパワエレ機器では短絡事故が発生しないことが理想ですが、稀に故障や誤動作によってパワーデバイスが短絡する場合があります。

パワーデバイスが短絡すると大電流によって発熱し、短絡条件やそのデバイスの定格電流の大小等にもよりますが、概ね数µsから数十µsの内にパワーデバイスは破壊します。デバイスが破壊すると短絡状態のままとなることが多く、パワエレ機器の故障や火災等の原因になります。そのため、通常はパワーデバイスが破壊する前にパワエレ機器の短絡保護回路によってパワーデバイスは短絡から保護されます。

しかし、短絡保護回路が短絡状態を検知し、パワーデバイスの短絡遮断が完了するまでには時間を要するため、少なくとも数µs程度の間、パワーデバイスは短絡状態に耐える必要があります。

したがって、短絡保護回路を設計するためにはパワーデバイスが短絡した場合にどのくらいの短絡時間であれば破壊せずに耐えられるか(=短絡耐量)を調べる必要があります。この短絡耐量を調べる試験を短絡試験と言います。

ここからは短絡試験の詳細について説明します。

短絡試験で測定する項目として短絡耐量時間(tsc)があり、パワーデバイスが短絡電流の通電を開始してから破壊するまでの時間のことを言います。短絡耐量時間はパワーデバイスの耐久性、信頼性を示す特性の一つになります。

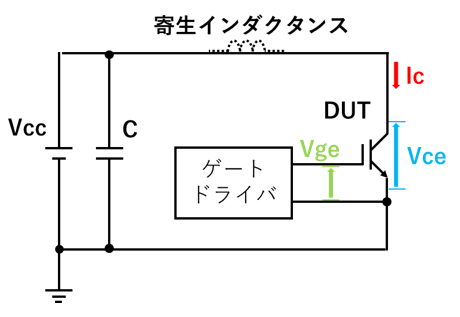

図1は短絡試験の回路図になります。ここでは例としてDUT(Device Under Test)にIGBTを使用していますが、MOSFETでも同様の試験回路です。

図1 短絡試験回路図

短絡試験ではDUTのオン時間を少しずつ延ばしていき、最終的に破壊するまで繰り返し測定し、短絡耐量時間を測定する場合が多いです。

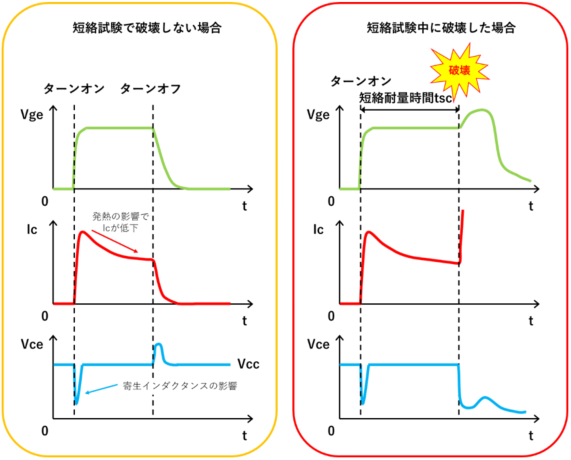

図2は短絡試験波形で、左側が短絡試験で破壊しない場合、右側が短絡試験中に破壊した場合の波形です。

図2 短絡試験の波形

DUTがオンした時に短絡し、コンデンサに蓄えられた電荷がDUTに流れ込むため、コレクタ電流Icが急激に増加します。オンした瞬間は寄生インダクタンスが一時的に電源電圧Vccを負担するため、コレクタ-エミッタ間電圧Vceはいったん下がり始めますが、すぐにIcが飽和するとともにVceはVccになります。その後、高電圧、大電流で通電するため、DUTが発熱し、Icが徐々に低下していきます。

図2の左側のように設定したオン時間が経過し、そのままターンオフして無事に遮断完了できれば問題ないですが、オン時間を延ばしていくと、やがて図2の右側のようにDUTが破壊してショート故障に至ります。ショート故障になるとIcが急増し、Vceは低下します。この変化をモニタしながら短絡耐量を求めています。

以上が短絡試験の内容です。

実作業では、上記試験内容に基づき安全対策に留意しながら測定を行います。

また、DUTが破壊した場合に必要以上に電流を流さないようにするため、コンデンサを回路から遮断するシステムを構築中です。

当社には、パワーデバイスの特殊な試験環境と、特殊な試験に対応できるエンジニアがいますので、短絡試験をはじめとする各種パワーデバイスの評価を必要とされる場合は、是非ご相談ください。

【関連リンク】

- 「パワーモジュール」評価サービス

- パワー半導体の評価は安全が第一!

- トランジスタの動作原理はイメージで実感しよう

- パワーエレクトロニクスって、どういうもの?

- パワーデバイス/モジュール評価(パワーサイクル試験)

- オシロスコープの基礎知識

- パワーエレクトロニクス講座

- パワーエレクトロニクス講座 新大阪で開催しています!

- 製品含有化学物質調査・環境負荷物質調査の代行サービス

- 製品含有化学物質調査の代行サービスを開始しました!

- 新人教育担当者の振り返り ~新人の成長は自身の成長!~

- コミュニケーションの秘訣は行動です♪

- 男性初の育児休暇を半年間とりました!

- WTIには頼りになる技術者がいっぱい

- 1on1面談を始めました

- WTIは文章指導にも力をいれています♪

- 鎖骨骨折で入院!?会社の制度に救われました

- WTIの新人教育、ただいま真っ最中![18年度バージョン]

- 新人採用

- 中途採用

WTIメールマガジンの配信(無料)

WTIエンジニアが携わる技術内容や日々の業務に関わる情報などを毎週お届けしているブログ記事は、メールマガジンでも購読できます。ブログのサンプル記事はこちら

WTIメールマガジンの登録・メールアドレス変更・配信停止はこちら

WTIの技術、設備、設計/開発会社の使い方、採用関連など、幅広い内容を動画で解説しています。