こんにちは。カスタム技術課の川原です。

自動計測システムや受託評価サービス向けの環境構築、社内向けのツール開発など様々な領域の技術を担当しています。

近年、自動車の電動化をはじめ、産業機器、太陽光発電システム、電源機器など、様々な分野でSiCパワーデバイスの採用が急速に広がっています。SiCパワーデバイスは高速スイッチングや高温動作が可能で、低損失・高効率な電力変換を実現できるという大きな利点を持っています。一方で、従来のSiデバイスと比較して、ゲート酸化膜界面の品質に課題があり、熱的/電気的なストレスによって特性(主にゲートの閾値電圧VGSth)が変動することが知られています。弊社ではこのような課題に対する試験の一つとしてAC-BTI試験の受託サービス提供に向けた試験環境の構築をしております。

弊社環境では JEITA/JEDEC/ECPE の規格に準拠した試験の他に、高温環境での試験にも対応します。

AC-BTI試験とは?

AC-BTI(Alternate current bias temperature instability)試験は、SiC MOSFETのゲートに正負のACバイアスを連続して印加した際のしきい値電圧(VGSth)変動を評価する試験です。

ゲートスイッチングによる特性変動はスイッチングサイクル数に依存する傾向があることが分かっており、アプリケーションにもよりますが、少なくとも10^11サイクル以上のストレスを加えて評価します。

AC-BTI試験は日本国内(JEITA規格)での呼称で、ほぼ同等の試験が各地域の規格団体によって規格化されています。

- JEITA(日本) EDR-4713 Ammed.1-付属書E:

AC-BTI(Alternate current bias temperature instability)- JEDEC(アメリカ) JEP195:

GSS (Gate switching stress)- ECPE(欧州) AQG-324:

DGS (Dynamic gate stress)表1. 試験条件例 (AQG-324 QL-06a(DGS) 試験準拠の例)

| 項目 | 値 |

| スイッチングサイクル数 | ≧ 10^11 |

| 試験温度 | 25 ℃ |

| VDS | 0 V |

| ΔVGS/Δt | 1 V/ns (オーバーシュートなし) |

| スイッチング周波数 | 50 kHz |

| ゲート電圧 | VGSON=VGSMAX 、 VGSOFF = VGSMIN |

試験における技術的課題

1.高スルーレートとオーバーシュート抑制の両立

AQG-324のDGS試験ではΔVGS /Δtはスルーレートが1 V/ns (オーバーシュートなし)、JEDECのJEP-195では0.1 V/ns ~ 0.3 V/ns 程度でオーバーシュート/アンダーシュート は0.5 V以下と記載がありますが、これは寄生インダクタンスなどの影響で実現は容易ではありません。

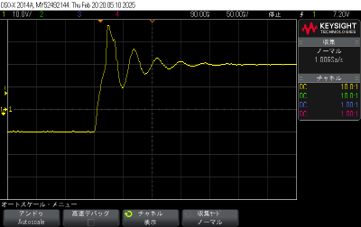

単純なゲートドライバでは下図のような激しいリンギングを起こすことがよくありますが、試験条件以上の過電圧を印加してしまうため、問題になります。

図 1 ストレス印加波形例1(オーバーシュート抑制未対策) dv/dt = 1.5 V/nsこの例では高速なMOSFETを出力段に使用することで約1.5 V/ns のスルーレートを実現していますが VGSHi = 20 V に対し、18 V 程度のオーバーシュートが発生しています。

VGSth測定値の安定性確保

- SiC MOSFETは直前に印加されていた電圧によってもVGSthの値が変動するため、ストレス電圧印加終了時のHi/Lowに一貫性を持たせるか、VGSth測定前にコンディショニングと呼ばれる一定の電圧パターンを加える処理を行った上で測定を行う必要があります。再現性の高いVGSth 測定には正確な試験/測定シーケンスの実行が必要です。

- 特に規格に謳われているわけではありませんが、VGSth が不安定であることから、ストレス印加終了からなるべく時間を空けずにVGSthを測定したいといった声をいただくこともよくあります。

弊社の取り組み

弊社はパワーデバイスの知見と自動計測システム構築の知見を併せ持っており、上記のような課題をクリアしつつ規格に準拠した試験環境の構築を行っております。

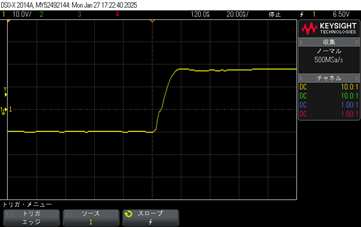

下図は 約1.5 V/ns のスルーレートを実現しながらもオーバーシュートほぼゼロを実現した例です。

図 2 ストレス印加波形例2(オーバーシュート抑制対策) dv/dt = 約1.5 V/ns

下図のようにスルーレート調整も可能です ※ 約0.67 V/ns

図 3 ストレス印加波形例3(オーバーシュート抑制対策+dv/dt変更) dv/dt= 約0.67 V/ns)

おわりに

AC-BTI試験は、特にSiC MOSFETの信頼性評価において重要な試験の一つとなっています。弊社では規格要求に準拠した試験環境を構築し、お客様の評価ニーズにお応えできるよう準備を進めております。

ご不明な点やご要望がございましたら、お気軽にお問い合わせください。【サービスページリンク】

【関連ブログ】

- DGS試験とは? ~次世代パワー半導体(SiC)のストレス試験~

- 信頼性試験について知ろう!(パワーサイクル試験編)

- 車載用電子部品の規格に準拠した試験サービス立ち上げに向けて

- AEC準拠試験に「計測評価プラットフォーム」を活用♪

- 導通抵抗モニタリングシステムのご紹介♪

- 「計測評価プラットフォームの活用推進」について!

【関連リンク】

【その他サービスリンク】

【iprosサイト】

【採用】

WTIでは、お客様に役立つ情報をYouTubeとFacebookページでも紹介させていただいております。

でご覧ください。

WTIメールマガジンの配信(無料)

WTIエンジニアが携わる技術内容や日々の業務に関わる情報などを毎週お届けしているブログ記事は、メールマガジンでも購読できます。ブログのサンプル記事はこちら

WTIメールマガジンの登録・メールアドレス変更・配信停止はこちら

こんにちは。カスタム技術課の川原です。

こんにちは。カスタム技術課の川原です。