E-Pad: Exposed die pad

みなさん こんにちは!第一技術部 構造設計課の有田です。

今回は部品裏面にE-Pad(Exposed die pad)がある半導体パッケージを実装する基板の放熱対策例を紹介いたします。半導体パッケージでは外部端子や樹脂を介して放熱を行っておりますが、近年の半導体パッケージの小型化や高機能化に伴い、パッケージ単体だけではなく、実装基板を含めた、熱設計が重要となっています。

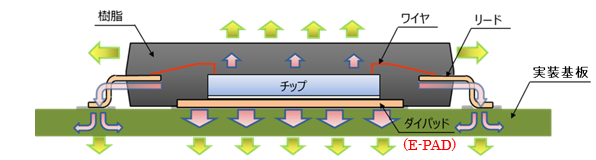

半導体パッケージ側での放熱対策として、図1のようなE-PADに半導体チップを搭載するパッケージがあります。

図1.E-PADを設けた半導体パッケージ

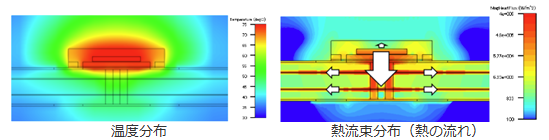

実装基板側ではE-PAD部分に放熱用のパッド(サーマルパッド)を設けます。サーマルパッドを設けることで半導体チップから実装基板への熱伝導効果は得られますが、それだけでは熱伝導経路が限定的(図2)で放熱は不十分となります。そこでサーマルパッドにサーマルビアを設けることで内層や半田面側へすぐに伝えることができ、図3のように半導体チップの熱を基板全体に拡散させることができます。

図2.サーマルビア無し 図3.サーマルビア有り

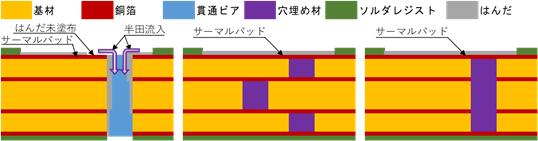

サーマルビアを設けることで放熱には効果的ですが、図4のようにサーマルパッドに通常の貫通ビアを設けるとサーマルパッドに穴が開き、リフローハンダ工程ではんだ流れによる実装不良問題が発生するデメリットがあります。

実装不良対策としてサーマルパッドの穴を塞ぐ工法に図5のビルドアップビアと図6の樹脂穴埋めビアがあります。

図4.貫通ビア 図5.ビルドアップビア 図6.樹脂穴埋めビア

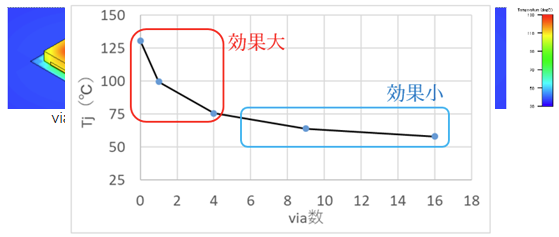

ビルトアップビアは設計の自由度が向上し高密度設計に向いていますが基板製造費用が高価になります。樹脂穴埋めビアは通常の貫通ビア+αの工程で製造できますのでビルドアップと比較し、費用を抑えることが可能です。また、樹脂穴埋めビアは貫通ビアと同様に基板表面から裏面まで直接繋がるのでビルドアップビアよりもビア個数を減らすことが可能です。図7のように、ビアの個数は多いほど放熱効果は高いですが一定数以上になると増加の効果が小さくなります。ビアの個数に対しては実装基板の設計制約(実装密度など)と放熱性能がトレードオフの関係にあるため、サーマルビアの個数は重要です。

図7.パッケージ下のビア個数と放熱効果

(熱シミュレーションによる検証結果)

いかがでしたでしょうか?皆様のご参考になれば幸いです。

WTIでは今回ご紹介したようなサーマルビアの最適個数など、熱シミュレーションを活用した基板設計や試作サービスを行っております。また半導体パッケージは大きくなると、実装信頼性など熱応力的な課題も出てくる場合があり、その場合は熱応力シミュレーションのサービスで改善提案も行っております。

お困りの際は、お気軽にお声掛けください。

【関連リンク】

【関連ブログ】

- 新人基板設計者が学ぶ!基板製造までの道のり!

- 基板製造装置の進化がすごい!工場見学に行ってわかったこと

- 基板設計を他社に依頼する時のポイント

- 基板メーカーからの問い合わせ事例(続編)~基板設計は基板メーカーの製造工程にあった調整も必要です

- 基板メーカーからの問い合わせ事例~基板設計は基板メーカーの製造工程にあった調整も必要です

- 基板設計勉強中!(社内アンテナ講座編③)

- 半導体ベアチップを用いた評価基板の設計や試作もできるんです!

- 続・基板製造を考慮した設計

- 基板の製造方法の紹介

- 基板設計勉強中!(社内アンテナ講座編②)

- 基板設計勉強中!(社内アンテナ講座編①)

- 基板設計勉強中!(DRC編)

- 基板設計勉強中!(部品配置検討編)

- BGAの基板設計(その3)

- BGAの基板設計(その2)

- BGAの基板設計(その1)

- 基板設計の手順と入社2年目エンジニアの醍醐味!

- ついに導入しました!基板設計CAD『CR-8000 Design Force』

- 実は関係が深い?基板構造と部品パッケージ

- 知ってます?基板の種類と用途

- 特性インピーダンスと基板設計

- ガーバーデータで基板改版?

- 基板設計は回路設計者との以心伝心が大事!

<WTIの採用ページは下記をご参照ください>

みなさん こんにちは!第一技術部 構造設計課の有田です。

みなさん こんにちは!第一技術部 構造設計課の有田です。