みなさん、こんにちは。

パワーデバイス設計課の中松です。今回はDGS試験についてお話しいたします。

DGSはDynamic Gate Stressの略で、AC-BTI(alternate current bias temperature instability)やGSI(gate switching instability)とも呼ばれます。SiC MOSFETではSiの場合と同様、正のゲートソース間電圧VGSを印加するPBTI(positive bias temperature instability)や、負のVGSを印加するNBTI(negative bias temperature instability)で閾値電圧のシフトが見られています。

しかし、SiC MOSFETの場合、正と負のVGSを交互に印加するDGS試験でPBTIやNBTIとはまた異なった挙動を示すことが報告されており、ここがSiの場合と異なっていて、SiC特有の重要な信頼性試験になります。また、SiC MOSFETの実際のアプリケーションでは正と負のVGSを印加することが一般的ですが、この条件はアプリケーションごとに異なるため、アプリケーションに応じた条件で試験することが重要になります。

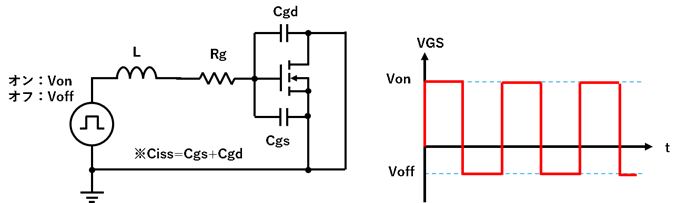

一番シンプルな試験回路は図1になります。ドレインソース間はショートします。単純にゲートドライバ等で正負の電圧を印加することでAC的なストレスを与えます。Rgはスイッチング速度を制限するゲート抵抗になります。

図 1 DGS試験の回路図例と試験波形

この回路ではゲート抵抗Rg、回路やデバイスの寄生インダクタンスL、デバイスの入力容量CissからなるRLC直列回路になっており、この3つの値によってVGS波形の形状が決まります。RLC直列回路の過渡応答について、詳細は電気回路の教科書等に記載されていると思いますので省略しますが、以下の3パターンになります。

(1) 減衰振動

(2) 臨界減衰

(3) 過減衰このうち(1)の減衰振動は振動を伴いますので、VGSのオーバーシュート、アンダーシュートが発生し、瞬時であっても試験条件以上の過電圧が発生するため問題になります。

例えば、欧州の車載向けパワーモジュール規格であるAQG324*1ではオン状態のVGSは最大電圧値、オフ状態のVGSは推奨最小電圧値で試験するようになっていますが、VGSが振動すれば当然これらの値を超えるため、試験として問題になります。したがって、(2)、(3)を満たす条件として、Cissはデバイス固有の値のため、Rgを大きくする、あるいはLを小さくする必要があります。ただし、Rgを大きくするとスイッチング速度が低下するため、dVGS/dtに規定がある場合は注意する必要があります。例えば、AQG324*1の場合では1 V/nsとなっております。また、この回路は電圧駆動のため、ゲート充放電終盤のゲート電流は小さくなり、一定速度で充放電ができないため、ゲートを一定速度で充放電したい場合は工夫が必要になります。

このようにDGS試験ではデバイスや試験条件に合わせて試験を行う必要があり、ノウハウが必要になります。弊社ではこのような試験に対する様々な知見がありますので、お気軽にご相談ください。

*1:AQG324:欧州の組織ECPEのワーキンググループによって車載向けパワーモジュール評価に関して策定された規格です。

【関連リンク】

- 人材採用(インターンシップ・新卒・中途)

- 車載用半導体向け信頼性試験サービス(AEC-Q101、AQG-324準拠)

- 電源(パワエレ)

- カーブトレーサ自動測定システム

- パワーサイクル試験

- WTIの技術講座

- 集合講座(会議室で講師がご解説します)

- オンデマンド講座(講座の動画にて学習できます)

- ライブ配信講座(ライブ配信にて講師がご解説します)

- パワーエレクトロニクス講座(集合講座)

- パワーデバイスの基礎講座(オンデマンド講座)

- パワーデバイスの基礎講座(ライブ配信講座)

- 電子回路の基礎講座PLUS(2日間コース)

- EMC基礎講座

WTIブログもご覧ください

- パワーエレクトロニクスって、どういうもの?

- 「パワー半導体」の信頼性試験について

- ダイオードのせん頭サージ電流(IFSM)とは

- 「パワー半導体」のスイッチング評価は難しい? ~その1~

- 「パワー半導体」のスイッチング評価は難しい? ~その2~

- パワーMOSFETのアバランシェ試験とは ~その1~

- パワーMOSFETのアバランシェ試験とは ~その2~

- パワーMOSFETのアバランシェ試験とは ~その3~

- パワーデバイスの短絡試験について

- 「パワー半導体」スイッチング評価の電流測定

- 「パワーデバイスの基礎講座」のご紹介

- CMOS[低耐圧MOSFET]とパワー半導体との違い

- パワー半導体の評価は安全が第一

- SiCデバイスを使って電源を高効率化してみました

- 電源設計技術者が見つからない時代 だから自社で育成する!

- いまさらなんですが、SiCって何がいいのでしょうか?

みなさん、こんにちは。

みなさん、こんにちは。